elettronica.live

27

'22

Written on Modified on

Mouser News

RISC-V: un'ISA open source, esente da royalty ed espandibile alla conquista del mercato

Sommario breve: Le ISA (Instruction Set Architecture) hanno subito modifiche di lieve entità nel corso degli ultimi quattro decenni, ma con l'avvento di RISC-V, un'ISA open source esente da royalty ed espansibile, lo scenario è destinato a mutare radicalmente.

Nel mondo dei processori l'introduzione di una nuovo ISA (Instruction Set Architecture) è un evento alquanto raro.

SEO Keywords: x86, MIPS, ISA, instruction set architecture, RISC, CISC, RISC-V, Microchip, AVR, Atmel, Atmel AVR, Arm, Intel, SoC, FPGA, SparkFun, SEEED

ISA dei processori: avanti adagio negli ultimi 40 anni

Per svariati decenni Intel e Arm hanno dominato il panorama delle architetture dei processori. Intel e la sua architettura x86 detiene una quota predominante nei settori delle workstation, dei computer desktop e dei server. Arm, dal canto suo, si è imposta come punto di riferimento in mercato molto ampi, come quelli dei dispositivi IoT, dell'elettronica di consumo e dei sistemi di automazione industriale. Altre architetture di microcontrollori e processori embedded, come AVR di Atmel e PIC/MIPS di Microchip, benché utilizzate in parecchi settori di nicchia, non sono riuscite a raggiungere una massa critica tale da poter competere con le due aziende dominanti, Il modello di vendita di licenze di proprietà intellettuali (IP) introdotto da Arm è stato adottato su larga scala dalla maggior parte dei produttori di MCU e MPU che operano nel campo dei sistemi embedded.

Tuttavia, in questi ultimi tempi si sta verificando un rapida trasformazione destinata ad avere importanti conseguenze e modificare le regole ampiamente consolidate che governano il mercato dei processori. I più importanti produttori stanno adottando celermente l'ISA RISC-V, di tipo open source, dopo aver riscontrato il crescente interesse dei loro clienti per i vantaggi economici e commerciali tipici dell'approccio open source. In questo articolo verrà descritta la genesi di RISC-V e sottolineati alcuni dei fattori che contribuiscono alla sua crescente diffusione. Verranno anche forniti alcuni esempi di prodotti, focalizzando l'attenzione su schede di valutazione, risorse di sviluppo e sull'ecosistema, in costante espansione, delle toolchain software.

ISA – Il collegamento reale tra l'hardware del processore e il software

Un'ISA (Instruction Set Architecture – ovvero l'insieme delle istruzioni che un processore è in grado di eseguire) fornisce l'interfaccia tra il software e l'hardware del processore. L'ISA definisce ogni aspetto delle modalità di interazione di un programma con l'hardware disponibile, compresa l'unità aritmetico-logica (ALU), i registri, la memoria e la logica di controllo. Essa inoltre specifica la lunghezza della parola, i tipi di dati supportati, nonché le modalità di indirizzamento delle locazioni di memoria e dei registri. In sintesi, un'ISA è un modello astratto di un processore.

Anche se esistono numerosi tipologie di ISA, a livello pratico le due più importanti sono CISC (Complex Instruction Set Computer) e RISC (Reduced Instruction Set Computer). Come suggerisce il nome stesso, l'architettura CISC contiene numerose istruzioni complesse e specializzate per varie applicazioni, alcune delle quali vengono utilizzate molto raramente. Un processore CISC, inoltre, prevede numerose modalità di indirizzamento e utilizza istruzioni di lunghezza variabile. La progettazione di processori basati sull'architettura CISC è più lunga e costosa, oltre a richiedere software e tool di programmazione più sofisticati. L'architettura x86 di Intel è un esempio di ISA CISC.

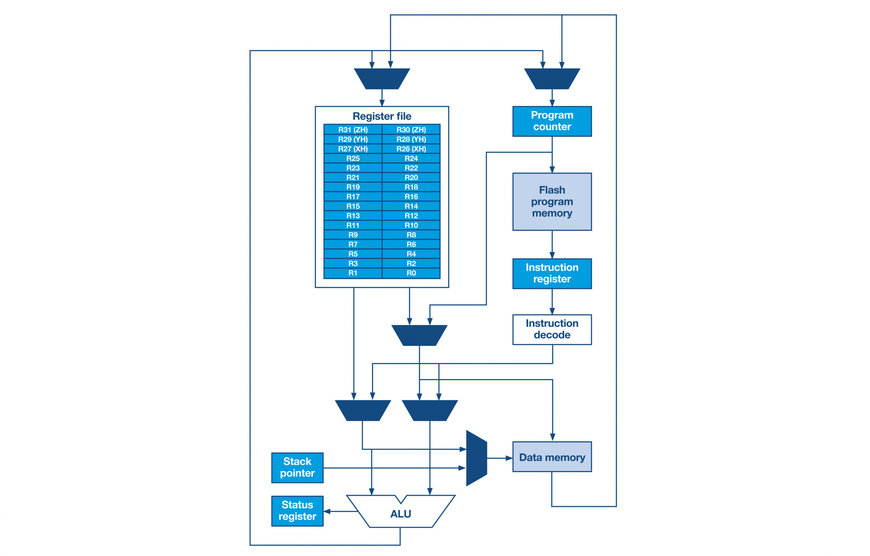

Un processore basato su architettura RISC (un esempio è riportato in figura 2) è molto più semplice e prevede un set limitato di istruzione che vengono utilizzate di frequente, un numero ridotto di modalità di indirizzamento e una dimensione fissa dell'istruzione. L'utilizzo di tecniche di pipeling delle istruzioni (in cui cioè l'esecuzione di una istruzione viene divisa in più fasi) permette di aumentare il throughput (ovvero la quantità delle istruzioni eseguite in un determinato intervallo di tempo). A differenza di un processore CISC che trasferisce gli operandi (i valori del dati) nella memoria per eseguire i calcoli, un processore RISC utilizza registri interni. Arm, AVR, PIC e MIPS sono alcuni esempi di ISA basate su RISC.

Esempio di architettura RISC di un microcontrollore AVR di Microchip.

ISA: i fattori che determinano il successo

Nella prosieguo dell'articolo l'attenzione sarà rivolta esclusivamente sui processori in architettura RISC. A questo punto è utile sottolineare che quando si parla di processore, in questo contesto si farà riferimento a qualsiasi dispositivo di elaborazione, come microcontrollori e microprocessori. Le ISA RISC più diffuse sono caratterizzate da lunghezze di parola di 8, 16 e 32 bit, mentre le ISA a 64 e 128 bit sono impiegate per applicazioni più specialistiche che richiedono prestazioni più elevate. La lunghezza della parola ha un impatto rilevante sulla progettazione dell'hardware, sulla velocità di funzionamento del processore e sulla capacità di memoria disponibile. Un ISA deve includere come minimo un'unità aritmetico-logica, una memoria e la logica di controllo. La ALU esegue le funzioni di calcolo aritmetico elementare, come addizione, confronto e sottrazione utilizzando registri oppure immediatamente al suo interno. L'indirizzamento della memoria può essere assoluto o indicizzato. La logica di controllo, infine, esegue il branching (salto) condizionale e non condizionale e altri compiti di indirizzamento.

Il set di istruzioni di un ISA è formato a un opcode (codice macchina) che specifica il compito (task) che deve essere eseguito, solitamente su un operando (o più operandi). Per esempio, all'interno dell'ISA AVR di Atmel/Microchip, l'istruzione ADC somma gli operandi contenuti in due registri e il valore del flag C (Carry- riporto) e inserisce il risultato nel registro di destinazione. La documentazione dell'ISA indicherà il numero dei cicli di clock o delle iterazioni del PC (Program Counter – contatore di programma) richieste da ogni istruzione. In un processore RISC, la maggior parte delle istruzioni verrà eseguita all'interno di un singolo ciclo di clock.

Per i produttori di microcontrollori (MCU) e microprocessori (MPU) lo sviluppo di un'ISA riveste un'importanza fondamentale nella progettazione dei loro prodotti. Per questo motivo, i set di istruzioni sono diventati proprietari, ovvero espressamente ideati per specifiche famiglie di dispositivi. Tra i numerosi esempi si possono annoverare AVR (8, 16, 32 bit) di Atmel/Microchip, PIC (8,16, 32 bit) di Microchip e MIPS (32, 64 bit).

All'inizio degli anni '90 Arm (Advanced RISC Machines), una spin-off di Acorn, ha “stravolto” il modello di business dominante nel settore delle MPU/MCU. L'approccio di Arm prevedeva la vendita di licenze di IP: in questo modo, gli incassi della società non erano ascrivibili alla fabbricazione e vendita di dispositivi, bensì al pagamento delle royalty. Il modello adottato da Arm è stato coronato da un rapido successo, in quanto i produttori di semiconduttori erano esentati dall'onere di dover effettuare lo sviluppo e il successivo porting delle loro ISA. Attualmente, la maggior parte dei produttori di semiconduttori fornisce processori basati sull'ISA Arm, mentre alcuni propongono anche dispositivi basati su un'ISA di tipo proprietario. Ciascuno di questi produttori paga una royalty ad Arm per ogni dispositivo venduto. Arm, dal canto suo, si assume l'onere del controllo del ciclo di vita e dello sviluppo su base continuativa dell'ISA.

Mentre ogni singola ISA ha i propri vantaggi e svantaggi, il successo di qualsiasi architettura di processore non si basa solamente sulle sue caratteristiche tecniche, ma anche sulla disponibilità di un ecosistema di tool di sviluppo software. Toolchain, ambienti di sviluppo integrati, compilatori debugger e middleware specifici per la particolare applicazione considerata rivestono un ruolo cruciale nella diffusione e nell'affermazione di un processore (e della relativa ISA).

L'avvento di un'ISA open source

Per i produttori di semiconduttori Arm ha creato un'ISA standard a partire dalla quale essi possono adattare e migliorare le opzioni di interfacciamento delle periferiche del dispositivo per soddisfare le esigenze della particolare applicazione considerata. Un approccio di questo tipo ha permesso ai vari costruttori che utilizzavano gli IP Arm di differenziare i loro prodotti. Nel caso delle ISA già presenti sul mercato, come AVR, PIC e così via, l'adozione su larga scala di Arm ha comportato una riduzione della loro quota di penetrazione nel mercato.

Per gli utenti che utilizzano i microprocessori, la decisione di adottare un'ISA Arm è sicuramente una scelta oculata, in quanto la presenza di parecchi produttori di processori di questo tipo permette di avere a disposizione numerosi opzioni di acquisto da fornitori alternativi (seconda sorgente) di prodotti simili. Anche la standardizzazione dello sviluppo attorno a una toolchian specifica rappresenta una scelta valida dal punto di vista commerciale.

In un comparto industriale che ha fatto propri numerosi concetti dell'approccio open source, il dominio delle ISA dei processori è sempre rimasto ancorato al concetto di sviluppo di tipo proprietario. Questo fino al 2010, anno in cui ha fatto la sua apparizione l'ISA RISC-V. Anche se concepita inizialmente presso l'Università della California (Berkeley) come ISA destinata a scopi puramente accademici, l'idea di adottare un approccio allo sviluppo basato sul concetto di open source si era rapidamente affermata. Il motivo di questa decisione derivava dalla constatazione del fatto che il progetto delle ISA non aveva subito sostanziali modifiche negli ultimi 40 anni. L'approccio basato sull'open source, per contro, oltre a stimolare una maggiore interazione e il riutilizzo del software, avrebbe incoraggiato i fornitori della toolchain dei produttori a garantire il supporto sul lungo termine. Essendo un'ISA di tipo open source, i produttori non dovevano pagare alcuna royalty e potevano aggiungere nuove istruzioni ed espansioni.

L'ISA RISC-V base e le estensioni associate sono ora sviluppate e gestite in cooperazione tra il mondo accademico e quello industriale. L'ISA RISC-V supporta lunghezze di parola di 32, 64 e 128 bit.

La costituzione, avvenuta nel 2015, di RISC-V Foundation da parte di un consorzio di aziende operanti nel settore dei semiconduttori ha rappresentato sicuramente una tappa importante nell'evoluzione di RISC-V. Le sue caratteristiche intrinseche, ovvero assenza di royalty ed espandibilità, hanno attirato l'attenzione dei costruttori. Le licenze concesse da Arm non prevedono la possibilità di modificare il set di istruzioni per soddisfare le specifiche di una particolare applicazione, a esempio per ridurre i consumi di potenza, che invece è contemplata dalla licenza RISC-V. Attualmente, RISC-V Foundation può contare sul supporto di oltre 750 aziende associate.

Poichè un gran numero di produttori di processori ha iniziato a manifestare un forte interesse per RISC-V, la community che si occupa dello sviluppo di tool software ha cominciato a prevedere il supporto per questa ISA nei propri ambienti di sviluppo integrati (IDE) e nelle proprie toolchain.

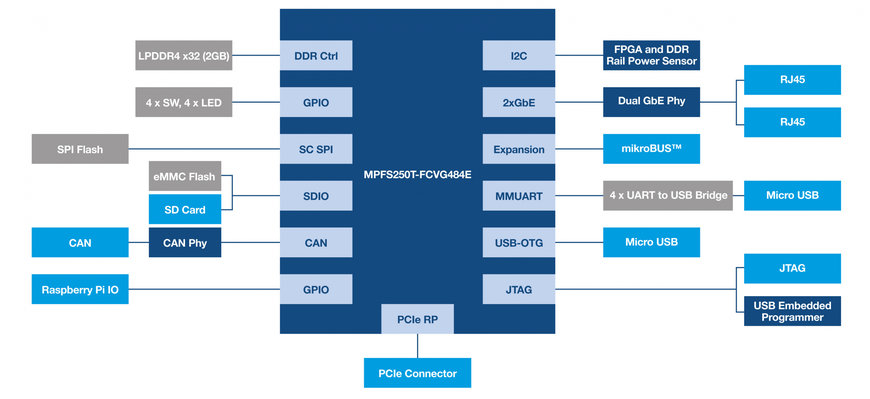

Schema a blocchi funzionale del kit di valutazione RISC-V per SoC PolarFire di Microchip.

Sviluppo con RISC-V: alcune soluzioni

Uno dei primi processori a 32 bit basato su RISC-V disponibile è stato il SoC Freedom E31 di SiFive, azienda fondata da alcuni tra gli ideatori dell'ISA RISC-V che si erano posti l'obiettivo di trasferire in tempi brevi le esperienza acquisite sul mercato. Al fine di incoraggiare la fase di prototipazione la società aveva avviato una campagna di crowdfunding per la realizzazione di una scheda di sviluppo a basso costo in formato Arduino denominato HiFive1. La scheda HiFive1 B di SiFive (Fig. 1) integra la connettività Wi-Fi e prevede una memoria flash da 32 Mb.

SEEED propone una scheda di sviluppo nel formato Feather/MKR, Sipeed Longan Nano, equipaggiata con un display LCD da 0,96” che utilizzata un core RISC-V a 32 bit di GidìgaDevices.

SparkFun fornisce invece RED-V RedBoard, una scheda di sviluppo simile a HiFive1 B, disponibile nel fattore di forma Arduino UNO-R3 ed equipaggiata con il SoC RISC-V E310 di SiFive.

Una piattaforma RISC-V molto più completa destinata a progettisti professionali è la scheda di sviluppo Icicle per SoC FPGA PolarFire di Microchip (Fig. 3).

Progettata per offrire una piattaforma di valutazione per il core RISC-V RV64 (che prevede cinque core) in grado di supportare Linux, il SoC PolarFire è equipaggiato con 256k elementi logici e 784 blocchi matematici. Ideale per la prototipazione di progetti real-time a basso consumo, destinati ad applicazioni che spaziano dai sensori IoT all'apprendimento automatico (machine learning), il kit Icicle include un'ampia gamma di interfacce per il collegamento di periferiche, tra cui HDMI, PCIe, USB, CAN, SPI e I2C. Tra le numerose interfacce di espansione opzionali di possono annoverare uno zoccolo mikroBUS e un connettore Raspberry Pi a 40 pin.

RISC-V: il viaggio continua

In un periodo di tempo relativamente breve, l'ISA RISC-V ha conosciuto un'ampia diffusione. A luglio 2020 la Fondazione ha celebrato il decimo anniversario dalla data dell'avvio dello sviluppo di RISC-V. Come riportato sul sito Web della Fondazione stessa, al momento attuale sono disponibili in commercio 12 SoC basati su RISC-V e 86 core.

In definitiva, RISC-V si è rapidamente imposta come un'alternativa concreta, espandibile e priva di royalty alle altre ISA presenti sul mercato.

www.mouser.com

Richiedi maggiori informazioni…